Korean chipmakers

Samsung to unveil 3D AI chip packaging tech SAINT to rival TSMC

The race for 3D chip packaging tech gets even fiercer as shrinking chips becomes increasingly challenging

By Nov 12, 2023 (Gmt+09:00)

3

Min read

Most Read

LG Chem to sell water filter business to Glenwood PE for $692 million

KT&G eyes overseas M&A after rejecting activist fund's offer

Kyobo Life poised to buy Japan’s SBI Group-owned savings bank

StockX in merger talks with Naver’s online reseller Kream

Meritz backs half of ex-manager’s $210 mn hedge fund

Samsung Electronics Co., the world’s largest memory chipmaker, plans to unveil an advanced three-dimensional (3D) chip packaging technology next year to compete with foundry leader Taiwan Semiconductor Manufacturing Company (TSMC).

The Suwon, South Korea-based chipmaker will use the technology – SAINT, or Samsung Advanced Interconnection Technology – to integrate memory and processors required of high-performance chips, including AI chips, in much smaller sizes.

Under the SAINT brand, Samsung plans to unveil three types of technologies – SAINT S, which vertically stacks SRAM memory chips and the CPU; SAINT D, which involves vertical packaging of processors such as the CPU and GPU and DRAM memory; and SAINT L, which stacks application processors (APs), people familiar with the matter said on Sunday.

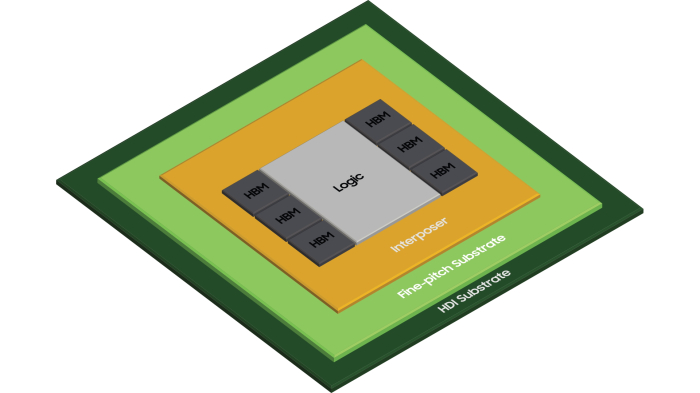

Current 2.5D packaging tech, in most cases, horizontally assembles different types of chips side by side.

Some of Samsung’s new technologies, including SAINT S, have already passed validation tests. However, Samsung will launch its commercial services next year after further tests with clients, sources said.

Packaging, one of the final steps in semiconductor manufacturing, places chips in a protective case to prevent corrosion and provides an interface to combine and connect already-made chips.

Leading chipmakers such as TSMC, Samsung and Intel Corp. are fiercely competing for advanced packaging, which integrates different semiconductors or vertically interconnects multiple chips. Advanced packaging allows multiple devices to be merged and packaged as a single electronic device.

Packaging technology can enhance semiconductor performance without having to shrink the nanometer through ultra-fine processing, which is technologically challenging and requires more time.

According to consulting firm Yole Intelligence, the global advanced chip packaging market is forecast to grow from $44.3 billion in 2022 to $66 billion by 2027. Of $66 billion, 3D packaging is expected to account for about a quarter, or $15 billion.

TSMC, CURRENT 3D PACKAGING LEADER

The technology has been rapidly increasing in line with growth in generative AI such as ChatGPT, which requires semiconductors that can process large data quickly.

The industry’s current mainstream is 2.5D packaging, which places chips as close together as possible to reduce data bottlenecks.

The world’s No. 1 contract chipmaker TSMC is also the leader in the global advanced packaging market with its decade-old 2.5D packaging technology.

TSMC is spending heavily to test and upgrade its 3D inter-chip stacking tech, SoIC, for its clients, including Apple Inc. and Nvidia Corp. TSMC said in July it will invest 90 billion Taiwanese dollars ($2.9 billion) in a new domestic advanced packaging plant.

Earlier this month, Taiwan's United Microelectronics Corp. (UMC), the world’s No. 3 foundry player, launched its wafer-to-wafer (W2W) 3D IC project to provide its clients with cutting-edge solutions for efficiently integrating memory and processors using silicon stacking technology.

UMC said its W2W 3D IC project, in collaboration with packaging firms such as ASE, Winbond, Faraday and Cadence Design Systems, is an ambitious undertaking that seeks to leverage 3D chip integration technology to address the specific requirements of edge AI applications.

Intel uses its next-generation 3D chip packaging tech, Foveros, to make advanced chips.

SAMSUNG’S CHIP PACKAGING ROADMAP

Samsung, the world’s No. 2 foundry company, has been accelerating the development of its chip packaging technology since it unveiled its 2.5D packaging technology H-Cube in 2021.

The 2.5D packaging tech allows logic chips or high-bandwidth memory (HBM) to be stacked on top of a silicon interposer in a small form factor, Samsung said.

The Korean company said in April it is offering a packaging turnkey service, handling the entire process from chip production to packaging and tests.

With its new SAINT technology, Samsung aims to improve the performance of AI chips for data centers and mobile APs with on-device AI functions, sources said.

Write to Jeong-Soo Hwang at hjs@hankyung.com

In-Soo Nam edited this article.

More to Read

-

Artificial intelligenceOn-device AI chips: New battleground for chipmakers

Artificial intelligenceOn-device AI chips: New battleground for chipmakersNov 05, 2023 (Gmt+09:00)

3 Min read -

Mergers & AcquisitionsSKC to acquire 12% stake in US chip packaging startup Chipletz

Mergers & AcquisitionsSKC to acquire 12% stake in US chip packaging startup ChipletzSep 11, 2023 (Gmt+09:00)

2 Min read -

Korean chipmakersSamsung set to supply HBM3, packaging services to AMD

Korean chipmakersSamsung set to supply HBM3, packaging services to AMDAug 22, 2023 (Gmt+09:00)

1 Min read -

Korean chipmakersSamsung Elec to provide HBM3, packaging service to Nvidia

Korean chipmakersSamsung Elec to provide HBM3, packaging service to NvidiaAug 01, 2023 (Gmt+09:00)

5 Min read -

Korean chipmakersSamsung, AMD extend partnership for next-generation graphic chips

Korean chipmakersSamsung, AMD extend partnership for next-generation graphic chipsApr 06, 2023 (Gmt+09:00)

3 Min read -

Korean chipmakersSamsung unveils 2.5D chip packaging tech for high-end products

Korean chipmakersSamsung unveils 2.5D chip packaging tech for high-end productsNov 12, 2021 (Gmt+09:00)

1 Min read

Comment 0

LOG IN